Title: 3 bit asynchronous Up/Down counter using flip flops.

**Aim:** To study 3 bit asynchronous Up/Down counter using flip flops.

Components: IC 7476 (-Ve edge triggered Dual J-K Flip-Flops), IC 7408 (Quad 2-input AND gates),

IC 7432 (Quad 2-input OR gates), IC 7404 (Hex Inverters), LEDs, Resister (220  $\Omega$ ).

**Equipment's and Miscellaneous:** Regulated DC power supply (0-25V), DMM, Breadboard, Connecting wires etc.

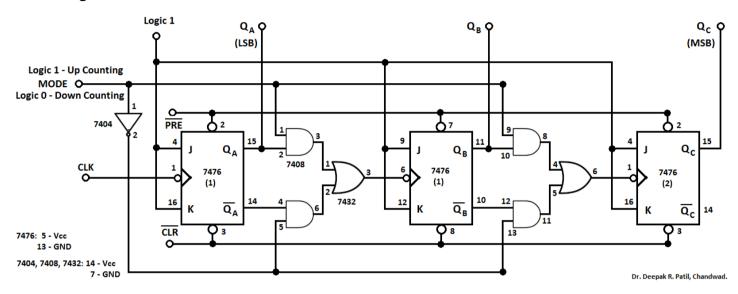

## **Circuit Diagram:**

**Note:** Connect series combination of 220 $\Omega$  resistor and LED between output and ground to see output.

#### **Observation Table:**

**Up Counter**

| Clock Input | Output           |       |                  |

|-------------|------------------|-------|------------------|

| Count       | $\mathbf{Q}_{C}$ | $Q_B$ | $\mathbf{Q}_{A}$ |

| 0           | 0                | 0     | 0                |

| 1           | 0                | 0     | 1                |

| 2           | 0                | 1     | 0                |

| 3           | 0                | 1     | 1                |

| 4           | 1                | 0     | 0                |

| 5           | 1                | 0     | 1                |

| 6           | 1                | 1     | 0                |

| 7           | 1                | 1     | 1                |

**Down Counter**

| Clock Input | Output           |                  |                  |

|-------------|------------------|------------------|------------------|

| Count       | $\mathbf{Q}_{C}$ | $\mathbf{Q}_{B}$ | $\mathbf{Q}_{A}$ |

| 7           | 1                | 1                | 1                |

| 6           | 1                | 1                | 0                |

| 5           | 1                | 0                | 1                |

| 4           | 1                | 0                | 0                |

| 3           | 0                | 1                | 1                |

| 2           | 0                | 1                | 0                |

| 1           | 0                | 0                | 1                |

| 0           | 0                | 0                | 0                |

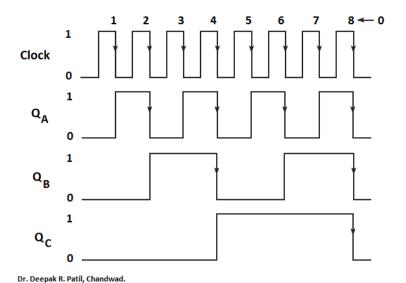

### **Timing Diagram:**

# A. Up Counter:

**B. Down Counter:** (Draw the timing diagram for down counter in Practical Sheet)

### **Result:**

3 bit asynchronous Up/Down counter is studied and verified its truth table.

(Do not write on Practical Sheet)

#### **Precautions:**

- 1. Always connect ground first and then connect Vcc.

- 2. The kit should be off before changing the connections.

- 3. Switch off the kit after the experiment.

#### **Procedure:**

#### A. For Up Counting:

- 4. Connect the circuit as shown in the diagram.

- 5. Connect  $\overline{PRE}$  input to the logic 1 i.e. +5V.

- 6. Connect  $\overline{CLR}$  input to the logic 0 i.e. 0V or ground to reset counter.

- 7. Connect  $\overline{CLR}$  input to the logic 1.

- 8. Connect Mode input to logic 1 for Up counting.

- 9. Apply the clock pulse to CLK input.

- 10. Observe the output and verify the observation table.

## **B.** For Up Counting:

- 1. Connect the circuit as shown in the diagram.

- 2. Connect  $\overline{CLR}$  input to the logic 1 i.e. +5V.

- 3. Connect  $\overline{PRE}$  input to the logic 0 i.e. 0V or ground to set counter.

- 4. Connect  $\overline{PRE}$  input to the logic 1.

- 5. Connect Mode input to logic 0 for Down counting.

- 6. Apply the clock pulse to CLK input.

- 7. Observe the output and verify the observation table.